GLoBaLReBeL

New Member

System . . .

AMD Ryzen 3700X

MSi Unify x570 Mobo

Cosair 3600 32GB Ram (2x16GB)

650 SeaSonic Titanium rated PS

other odds and ends

I've read through at least the last 8 recent pages in the forum and couldn't find anything on this so hoping someone can assist.

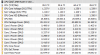

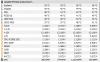

I am in the process of OC'n my 3700X and want to be sure that I am paying attention to the correct voltage readings in HWiNFo for the ACTUAL voltage the CPU is getting. In my BIOS I can set it to an all core clock OC, and set the VCore to the (AMD) recommend max voltage of 1.325. Once in windows I launch HWiNFo and start benching to see what Vdroop I get when pushing the system to the max. I want to know what reading should I be looking at to determine the actual voltage that the CPU is getting?

If I look at 'SVI2 TFN', it pretty much stays at 1.325, but if I focus on the 'Core x VID' I see the voltage drop to 1.2xx during all core workloads. If I want to get the most out of my all core OC, then I need to use LLC to help with Vdroop but I don't know which reading to base my choice off of. If I base it off of 'Core x VID', then I know I should start increasing my LLC modes up until I get it to stay stable at 1.325 under all core load in my 'Core x VID'. If I base it off the SVI2 TFN then I don't want to use LLC as it doesn't really drop below 1.325.

My thought process is...

(Turn off PBO, cool'N'quiet,C-States, etc as I am just doing all core OC and don't need any of this as I want it to act the exact same way at all times during use)

1. Set multiplier for CPU

2. Set Vcore to value (for me 1.325)

3. Launch Windows and HWiNFo

4. Start bench and look at numbers

5. If numbers drop below 1.325, then increase multiplier until unstable and once unstable increase LLC mode in BIOS and retest

Step 5 is where I need to know what voltage value/reading I should be looking at in order to ID the voltage flucuation change from the LLC mode change.

I apologize if this has been coverd, but I wasn't able to find it anywhere.

AMD Ryzen 3700X

MSi Unify x570 Mobo

Cosair 3600 32GB Ram (2x16GB)

650 SeaSonic Titanium rated PS

other odds and ends

I've read through at least the last 8 recent pages in the forum and couldn't find anything on this so hoping someone can assist.

I am in the process of OC'n my 3700X and want to be sure that I am paying attention to the correct voltage readings in HWiNFo for the ACTUAL voltage the CPU is getting. In my BIOS I can set it to an all core clock OC, and set the VCore to the (AMD) recommend max voltage of 1.325. Once in windows I launch HWiNFo and start benching to see what Vdroop I get when pushing the system to the max. I want to know what reading should I be looking at to determine the actual voltage that the CPU is getting?

If I look at 'SVI2 TFN', it pretty much stays at 1.325, but if I focus on the 'Core x VID' I see the voltage drop to 1.2xx during all core workloads. If I want to get the most out of my all core OC, then I need to use LLC to help with Vdroop but I don't know which reading to base my choice off of. If I base it off of 'Core x VID', then I know I should start increasing my LLC modes up until I get it to stay stable at 1.325 under all core load in my 'Core x VID'. If I base it off the SVI2 TFN then I don't want to use LLC as it doesn't really drop below 1.325.

My thought process is...

(Turn off PBO, cool'N'quiet,C-States, etc as I am just doing all core OC and don't need any of this as I want it to act the exact same way at all times during use)

1. Set multiplier for CPU

2. Set Vcore to value (for me 1.325)

3. Launch Windows and HWiNFo

4. Start bench and look at numbers

5. If numbers drop below 1.325, then increase multiplier until unstable and once unstable increase LLC mode in BIOS and retest

Step 5 is where I need to know what voltage value/reading I should be looking at in order to ID the voltage flucuation change from the LLC mode change.

I apologize if this has been coverd, but I wasn't able to find it anywhere.