Timur Born

Well-Known Member

Hello.

There are three oddities about "Core Clocks" that make me wonder about accuracy and even reliability of the measurements. The following screenshots are on a 13900K. I may be understanding these wrong, though?!

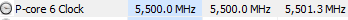

1. Core Clocks may not catch maxima that Effective Clocks do catch.

True maximum 5600:

Expect behavior: Core Clocks' maximum should not be below Effective Clocks' maximum (or even its average).

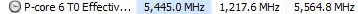

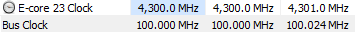

2. "Bus-clock based" sometimes calculates non-integer values, even when "periodic polling" is disabled and the bus-clock was measured as 100.000 MHz at startup.

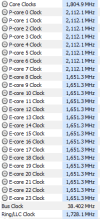

Maximum values:

Expected behavior: Core Clocks should only use multiples of the startup Bus Clock value when "periodic polling" is disabled.

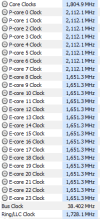

3. Disabling "Bus-clock based" leads to unusable values (may need restart to reproduce).

100% C0 residency:

Expected behavior: HWinfo should be able to measure the Core Clocks without being Bus Clock based, or the tooltip should clarify that this may not work on new CPUs (instead of just stating the defaults).

Thanks and all the best!

There are three oddities about "Core Clocks" that make me wonder about accuracy and even reliability of the measurements. The following screenshots are on a 13900K. I may be understanding these wrong, though?!

1. Core Clocks may not catch maxima that Effective Clocks do catch.

True maximum 5600:

Expect behavior: Core Clocks' maximum should not be below Effective Clocks' maximum (or even its average).

2. "Bus-clock based" sometimes calculates non-integer values, even when "periodic polling" is disabled and the bus-clock was measured as 100.000 MHz at startup.

Maximum values:

Expected behavior: Core Clocks should only use multiples of the startup Bus Clock value when "periodic polling" is disabled.

3. Disabling "Bus-clock based" leads to unusable values (may need restart to reproduce).

100% C0 residency:

Expected behavior: HWinfo should be able to measure the Core Clocks without being Bus Clock based, or the tooltip should clarify that this may not work on new CPUs (instead of just stating the defaults).

Thanks and all the best!

Last edited: