h4rp00n33r

New Member

Hello folks!

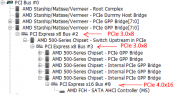

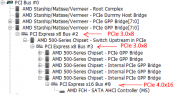

I'm struggeling with the representation of the PCI BUS hierarchy in HWiNFO64. Here's an example:

Thanks for your help in advance!

I'm struggeling with the representation of the PCI BUS hierarchy in HWiNFO64. Here's an example:

- PCIe Bus #2 works with PCIe 3.0x8.

- PCIe Bus #3 is connected to PCIe Bus #2 and works with PCIe 3.0x8. So far, so good.

- PCIe Bus #8 works with PCIe4.0x16. But how can this work when it is connected to PCIe Bus #3 which runs only PCIe 3.0x8? Following the hierachy of the diagram, PCIe Bus #2 and PCIe Bus #3 are bottle necks regarding the bandwidth, aren't they?

Thanks for your help in advance!