Timur Born

Well-Known Member

Hello.

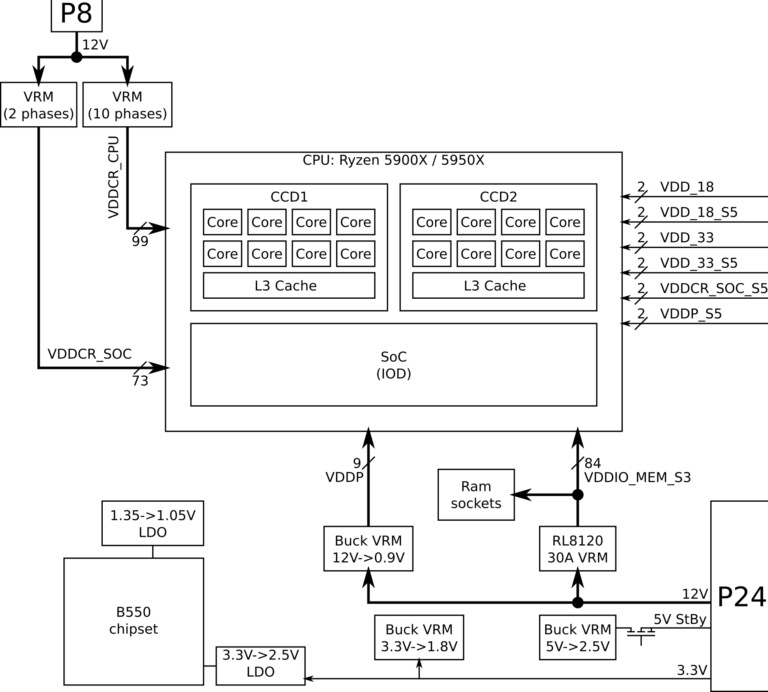

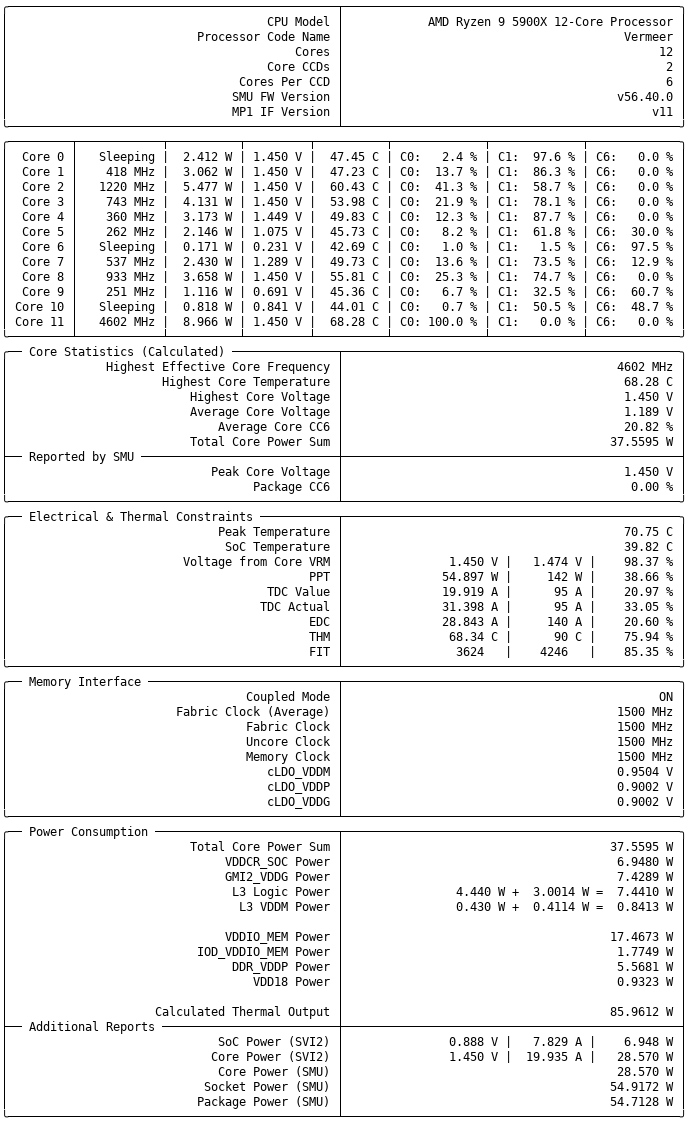

I wonder why on Zen 3 (5900X) the CPU Package Power (and CPU PPT) is always 20 watts over Core + SoC in all load states? And why is there no sensor corresponding to these 20 watts of power consumption?

CPU Package Power also reads higher than both PIN and POUT, which I assume speak to the lacking quality of corresponding VRM sensors (they only report in broad steps)?

I wonder why on Zen 3 (5900X) the CPU Package Power (and CPU PPT) is always 20 watts over Core + SoC in all load states? And why is there no sensor corresponding to these 20 watts of power consumption?

CPU Package Power also reads higher than both PIN and POUT, which I assume speak to the lacking quality of corresponding VRM sensors (they only report in broad steps)?