pha

Member

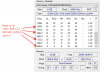

For example DDR4-2133P can operate at 1067 MHz with CL15 and CL16.

And there is no 1000Mhz frequency

[attachment=3471]

(HWInfo v6.06.3770)

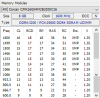

Here is JEDEC JESD79-4 specs for 2133 memory

[attachment=3473]

Correct values for my module is

[attachment=3472]

(Thanks Thaiphoon Burner)

And there is no 1000Mhz frequency

[attachment=3471]

(HWInfo v6.06.3770)

Here is JEDEC JESD79-4 specs for 2133 memory

[attachment=3473]

Correct values for my module is

[attachment=3472]

(Thanks Thaiphoon Burner)